Scientists develop analogue chip to cut data-center energy use and accelerate AI

Source: interestingengineering

Author: @IntEngineering

Published: 1/21/2026

To read the full content, please visit the original article.

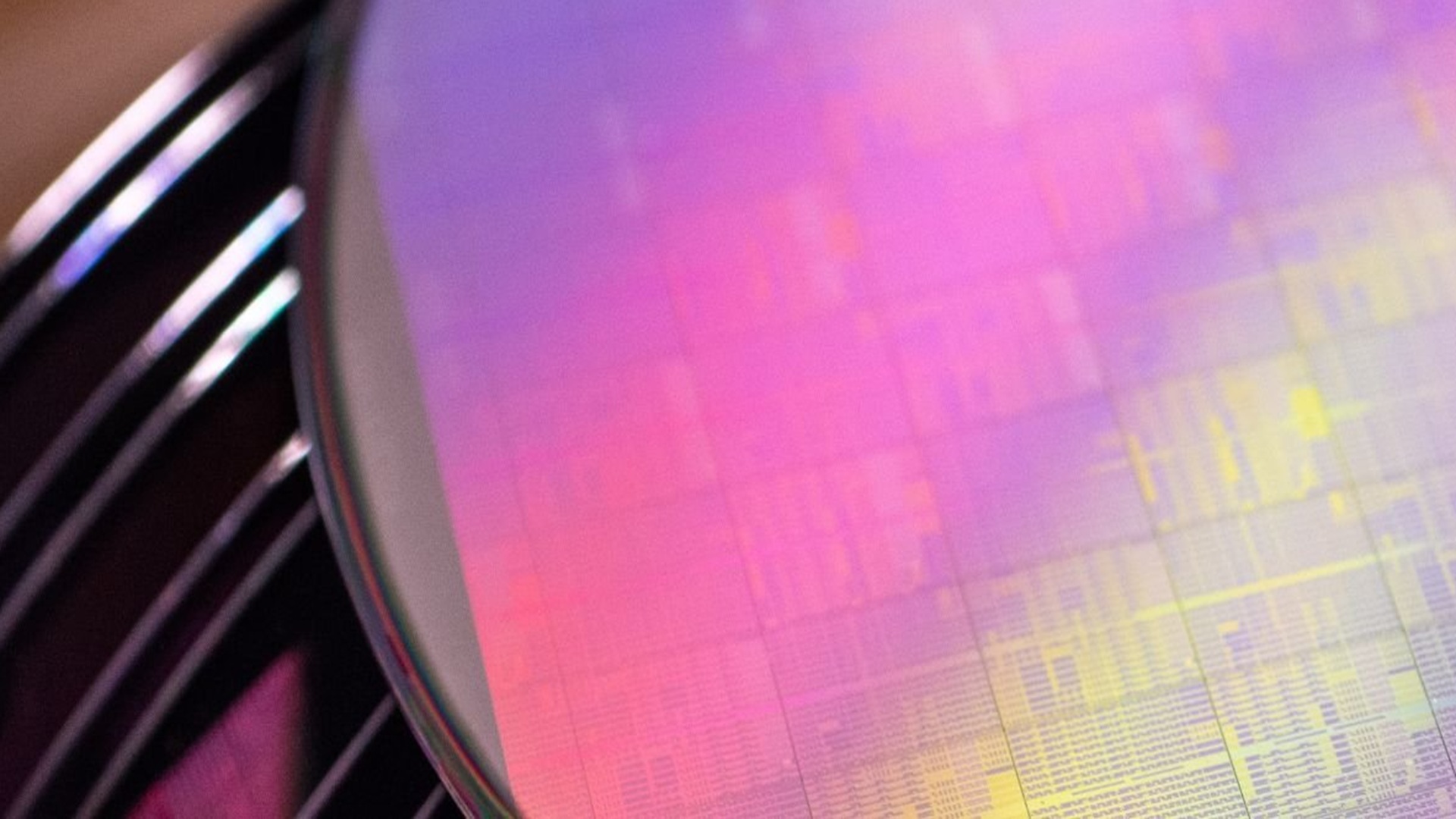

Read original articleResearchers at Politecnico di Milano, led by Professor Daniele Ielmini, have developed a novel analogue in-memory computing chip designed to drastically reduce energy consumption and accelerate computations in data centers and high-performance computing systems. Unlike traditional digital computers that expend significant energy moving data between memory and processors, this chip performs calculations directly within memory arrays, cutting internal data traffic. Built using standard CMOS technology, the fully integrated analogue accelerator employs two 64-by-64 arrays of programmable resistive memory cells combined with on-chip analogue components like operational amplifiers and analogue-to-digital converters. This architecture enables it to solve both linear and non-linear equations efficiently.

Testing showed the chip matches the accuracy of conventional digital systems while consuming up to 5,000 times less energy, offering lower latency and a smaller silicon footprint. The development is part of the ERC-funded ANIMATE project, which focuses on advancing closed-loop in-memory computing (CL-IMC) technology. The chip’s energy-efficient design holds promise for applications

Tags

energyanalogue-computingin-memory-computingCMOS-technologydata-center-energy-efficiencyAI-accelerationresistive-memory-cells