US engineers develop 3D chip that offers order-of-magnitude speed gains

Source: interestingengineering

Author: @IntEngineering

Published: 12/14/2025

To read the full content, please visit the original article.

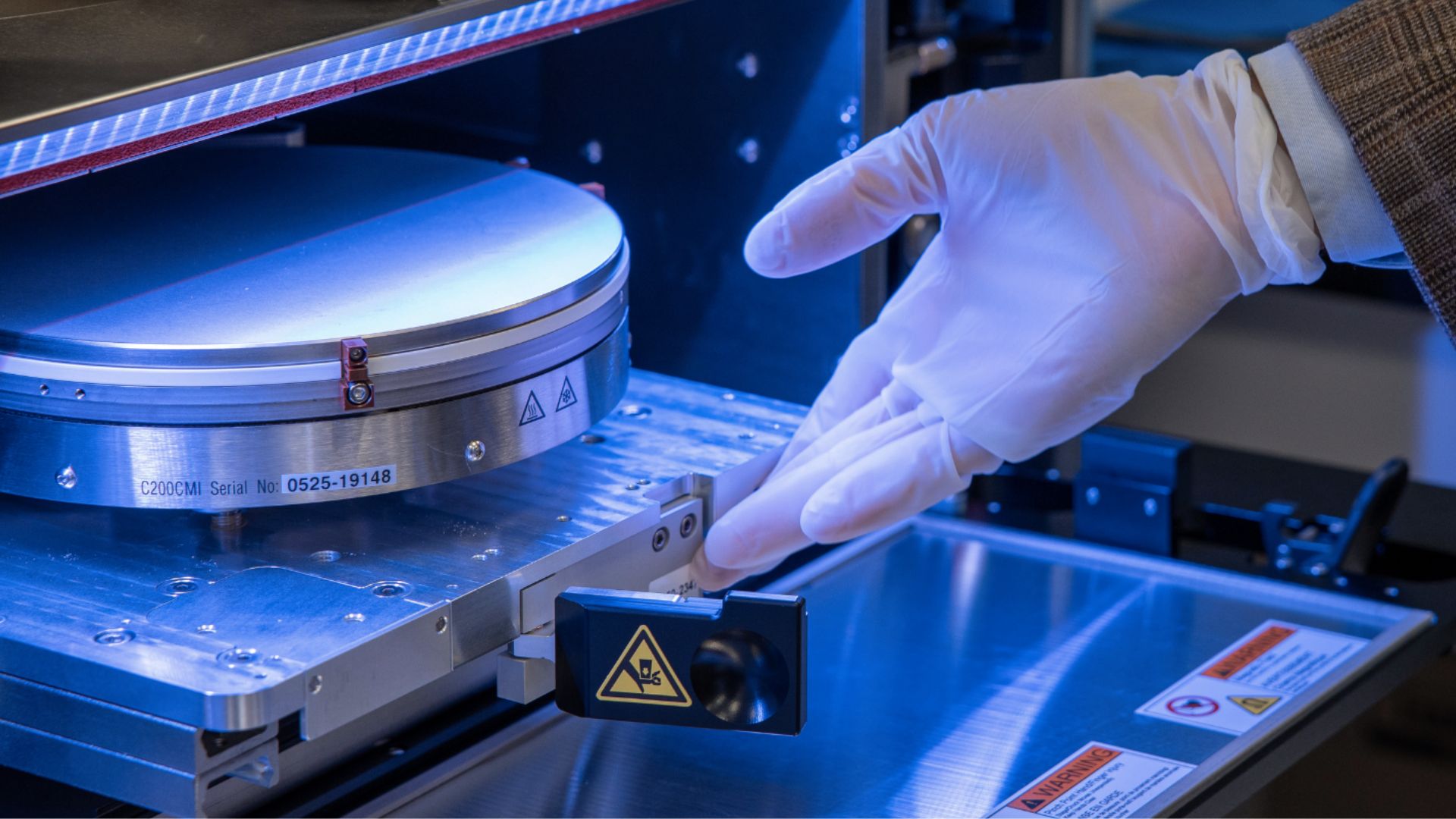

Read original articleUS engineers from Stanford, Carnegie Mellon, University of Pennsylvania, and MIT, in collaboration with SkyWater Technology, have developed a novel 3D multilayer computer chip architecture that significantly outperforms traditional 2D chips. Unlike conventional flat chips where components and memory are spread out on a single surface, this new design stacks ultra-thin layers vertically, interconnected by dense vertical wiring that enables rapid data movement. This architecture effectively overcomes the "memory wall" bottleneck—where processing speed outpaces data delivery—by integrating memory and computation closely in a vertical arrangement, akin to elevators in a high-rise building facilitating fast travel between floors.

Early hardware tests show the prototype chip achieves roughly a fourfold speed improvement over comparable 2D chips, while simulations of future versions with more layers predict up to a twelve-fold gain on real AI workloads, including those based on Meta’s LLaMA model. The design also promises dramatic improvements in energy-delay product (EDP), balancing higher throughput with lower energy

Tags

semiconductor3D-chipAI-hardwarecomputer-architecturevertical-integrationchip-innovationmemory-wall